电路中上拉电阻有必要吗?

而在51单片机系统中,不添加上拉电阻并不影响使用,并且也能够正确读写数据。以51单片机为例,除了P0口,另外3个口内部都有弱上拉。

所以似乎外部不用再加上拉电阻也可以。但是毕竟单片机内部上拉电阻能力有限,只能微弱上拉。

另外对于很多单片机,其内部有上拉电阻,但是无一例外,上拉电阻的组织是比较大的,也就是说其上拉能力有限。 根据I2C总线规范,总线空闲时两根线都必须为高:这条准则必须严格遵守,这是之所以规定空闲时必须为高的一个原因,如果要保持“低”,那么就不可能成为“多主”总线的。

上拉电阻的问题:各个I2C接口工作时只检测高、低电平即可,上拉电阻实际上不是十分必要。但问题是,如果直接采用电源的来实现高的话,一旦其他器件拉低就有可能发生危险。

上拉电阻有保护作用。如果确信直接采用电源没问题(比如有短路保护等),也可进行尝试。

问题的关键在于主器件要能正确的拉低或置高,从器件要能明确地区分高、低即可,这是问题的关键,另外时序问题同样不能混乱。 电阻大小的问题:这牵涉到两方面的问题,首先是功耗的问题,其次是速度的问题,二者互相矛盾,如果想尽量提高速度,那么必然牵涉到总线电容问 题。

上拉电阻与总线的电容形成RC,高速时将直接影响通讯。因为总线拉高时有充电时间以及高电平的阀值,如果还没有充电到足以保证从器件能够识别的高电平 的阀值时,主器件就以为完成了一个总线动作的话,那么通讯肯定是不能进行。

如果想尽可能降低功耗,那么就要尽量增大电阻以最大可能的减小电路各部分消耗电流。从而实现整体降低功耗!但不可能无限大,否则充电时间会很成问题。

您可能还喜欢这些产品

变压器在电路中的主要作用有哪些

变压器在电路中的主要作用有哪些变压器是利用电磁学的电磁感应原理将电能从一个电路传输到另一个电路的电气设备。它可以将一个电压的交流能量转换为同一频率下另一电压的交流能

- 陶瓷电容器有正极和负极吗?陶瓷电容器上的数字代表什么

陶瓷电容器有正极和负极吗?陶瓷电容器上的数字代表什么陶瓷电容器是一种以陶瓷材料为介质的常见电容器,具有体积小、频率响应范围宽、耐高温等

汽车上拉电阻的作用原理

汽车上拉电阻的作用原理上拉是通过电阻器将不确定信号箝位到高电平,同时起到电流限制的作用。类似地,下拉通过电阻器将不确定信号箝位到低电平。在由上

- 电阻的大小与温度有关吗

电阻与温度之间的关系当电荷在导体中移动时,它们会受到分子和原子等其他粒子的碰撞和摩擦。这些碰撞和摩擦的结果形成了导体对电流的阻碍。这种

电阻的功率大小有影响吗

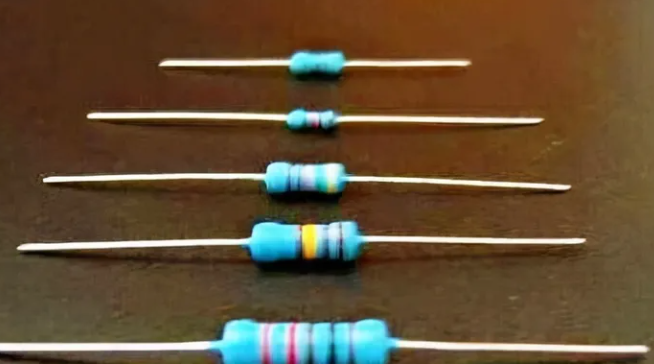

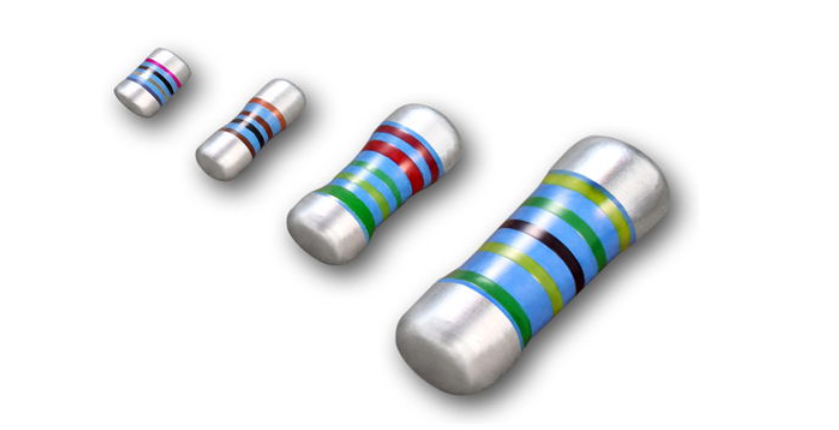

电阻的功率大小有影响吗电阻越高,功率就越大吗?电阻器有许多类型,常用的电阻器包括:;碳膜电阻、金属膜电阻、氧化物膜电阻、玻璃釉电阻、合成碳膜电阻,绕线电阻、

汽车水箱风扇有电容吗

汽车水箱风扇有电容吗晶圆电阻器及其应用范围简介晶圆电阻器是一种圆柱形、无电感、无铅金属膜电阻器,具有高稳定性、高精度,引脚的尺寸和间距与SMD电阻器焊盘相似,

水泵无力与电容有关吗

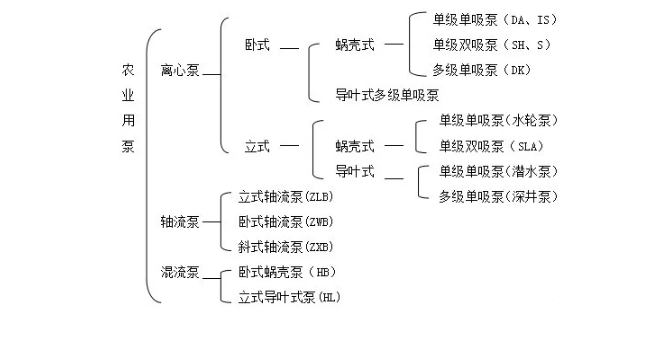

水泵无力与电容有关吗水泵的基础知识第一节 水泵用途及分类一、定义和用途泵是一种抽送能量液体的机械。就是把原动机的机械能转换为所抽送液体位能的机器。它在动力机

电容会爆炸吗?威力有多大?

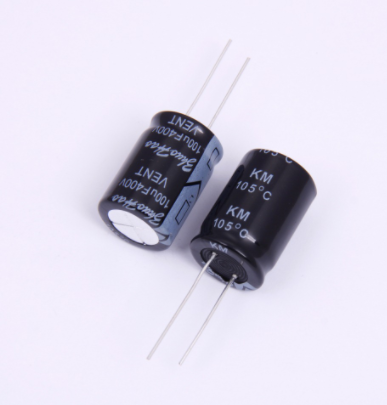

电容会爆炸吗?威力有多大?当电容器施加的电压超过其耐受电压时,或当极性电解电容器的电压极性反转时,电容器的泄漏电流将急剧上升,导致电容器的内部热量增加,电解质将

台湾光颉在那些地方有厂吗?

台湾光颉在那些地方有厂吗?台湾光颉工厂在台湾新竹。地址是:新竹縣湖口鄉新竹工業區北路70號

电解电容是有极性的吗

电解电容是有极性的吗有极元件是指对施加在其电极上的电源的极性的要求,要么是正极(高电位),要么是负极(低电位),并且不能颠倒。电解电容器是一种具有极性的电

法拉电容对汽车的影响有多少

法拉电容对汽车的影响有多少超级法拉电容器在汽车中的最佳应用是辅助电池,它被组装成超级电容器组。一般电压为15V,与蓄电池并联。它可以提供起动机瞬间启动所需

- 汽车音响加装电容到底有用吗?从电阻角度深度解读

从汽车电阻视角看音响电容的实际价值很多车主在加装音响电容后声称“声音更稳、低音更有力”,但这是否真的源于电容本身?本文将从汽车电阻系统

电路中三极管有什么不同

电路中三极管有什么不同三极管有各种类型,主要是为了适应不同的电路。根据频率,低频电路有低频三极管,高频电路有高频三极管,它们通过电流、大电流、

- 为什么保险丝的电阻率高?保险丝有电阻值吗?

为什么保险丝的电阻率高?保险丝有电阻值吗?熔断器,也称为电流熔断器,在IEC127标准中被定义为“熔断器连接”。它主要起过载保护的作用。在电路

可以用有缘晶振替换无源晶振吗

可以用有缘晶振替换无源晶振吗理论上,这是可能的。但不能直接替换。有源晶体振荡器必须至少有三个引脚,即VCC+、VCC-和信号输出。无源晶体振荡器只需要两个引脚。有源晶体振荡

为什么贴片电容上没有标注数值?

为什么贴片电容上没有标注数值?贴片电阻一般都有印代码,无论是E-24系列或E-96系列的电阻,可以都通过代码区别出其系列,并查出相应阻值。而PCB上的贴片电容几乎都没有印代码

热敏电阻主要应用及分类有哪些

热敏电阻主要应用及分类有哪些NTC热敏电阻主要用于汽车、医疗保健、家用电器、通信、计算机和办公自动化设备,以及消费电子产品和集成电路/模块。按产品应用范围划分,可分为:

电感阻抗公式适用以脉冲电路的计算吗?

电感阻抗公式适用以脉冲电路的计算吗?加载其电感量的计算公式:线圈公式:阻抗(ohm) = 2 * 3.14159 * F(工作频率) * 电感量(mH),设定需用 360ohm 阻抗,因此: 电感量(mH) = 阻抗 (ohm) ÷ (2*3.14159) ÷ F (

- 电路板上电阻怎样看大小

怎么看电路板上电阻的大小?有几种方法。首先,用万用表测量电阻。1.用电阻测量时,必须断电或烧表。2、根据被测电阻标称值的大小来选择量程。3.