如巧妙的减少甚至避免单机片干扰

1.I/O口有上拉电阻,上拉电阻阻值就是I/O口的输入阻抗。人们大多用4K-20K电阻做上拉,(PIC的B口内部上拉电阻约20K)。

由于干扰信号也遵循欧姆定律,所以在越存在干扰的场合,选择上拉电阻就要越小,因为干扰信号在电阻的电压就越小。由于上拉电阻越小就越耗电,所以在用家电设计上,上拉电阻一般是在10-20k,而在强干扰场合上拉电阻甚至可以低到1K.(如果在强干扰场合要抛弃B口上拉功能,一定要用外部上拉。

) 2.I/O口与其他数字电路输出脚相连。此时I/O口输入阻抗就是数字电路输出口的阻抗,一般是几十到一百欧。

可以看出用数字电路做中介可以把阻抗减低到最理想,在许多工业控制板上可以看见大量数字电路就是为了保证性能和保护MCU. 3.I/O口并联了小电容。 由于电容是通交流阻直流的,并且干扰信号是瞬间产生,瞬间熄灭的,所以电容可以把干扰信号滤除。

但是代价是造成I/O口收集信号的速率下降,比如在串口上并联电容绝不可取的,因为电容会把数字信号当干扰信号滤除掉。 对于一些特殊器件,如检测开关,霍尔元件等是能够进行并联电容设计的,这主要是因为开关量的变化较为迟缓,并不能形成很高的速率,所以即便电路中并联电容,对信号的采集也是不会有任何影响的。

。

您可能还喜欢这些产品

如何使用电容抑制电磁干扰

如何使用电容抑制电磁干扰电容是电路中最基本的元件之一,使用电容器过滤电路上的高频干扰并解耦电源是所有电路设计者所熟悉的。然而,随着电磁干扰问题的日益突出,

干扰的耦合方式都有哪些

干扰的耦合方式都有哪些干涉耦合模式干扰源产生的干扰信号通过某个耦合信道对电子控制系统产生电磁干扰。干扰的耦合模式只不过是通过电线、空间、公共线路等作用于电子

铝电解电容容量减少的主要原因是什么

铝电解电容容量减少的主要原因是什么一般认为,铝电解电容器容量下降的主要原因有以下三点:1.导销与铝箔接触不良,导致接触电阻增大,容量衰减,如铆接厚度过大,阳极铝箔粉过多,

- 如何快速区分贴片电阻与贴片二极管?实用技巧与检测方法分享

引言:为什么需要区分贴片元件?在现代电子维修与PCB设计中,贴片元件体积小、种类多,容易混淆。尤其在更换元器件或排查故障时,若将贴片电阻误

- 如何优化电流感应芯片电阻的电路设计?实用技巧全解析

优化电流感应电阻电路设计的五大关键点1. 选择合适的阻值以匹配芯片量程电流感应芯片通常有最大允许压降(如100mV),因此需根据预期最大电流计算

- 如何快速分辨大功率贴片电阻的功率值?实用技巧全解析

如何快速分辨大功率贴片电阻的功率值?实用技巧全解析在现代电子产品中,大功率贴片电阻广泛应用于电源管理、电机驱动、LED恒流等高电流场景。由

- 如何正确选择与安装家庭电路保险丝?避坑指南

家庭电路保险丝选型与安装的科学指南家庭用电安全依赖于合理的电气保护装置配置,尤其是保险丝的选择与安装。本文从技术参数、应用场景及常见误

- 1欧姆等于多少毫欧?详解电阻单位换算关系

1欧姆等于多少毫欧?单位换算核心解析在电子工程和电路设计中,电阻单位的准确理解至关重要。其中,欧姆(Ω)与毫欧(mΩ)是常见的电阻单位,尤

- 贴片电阻106阻值是多少

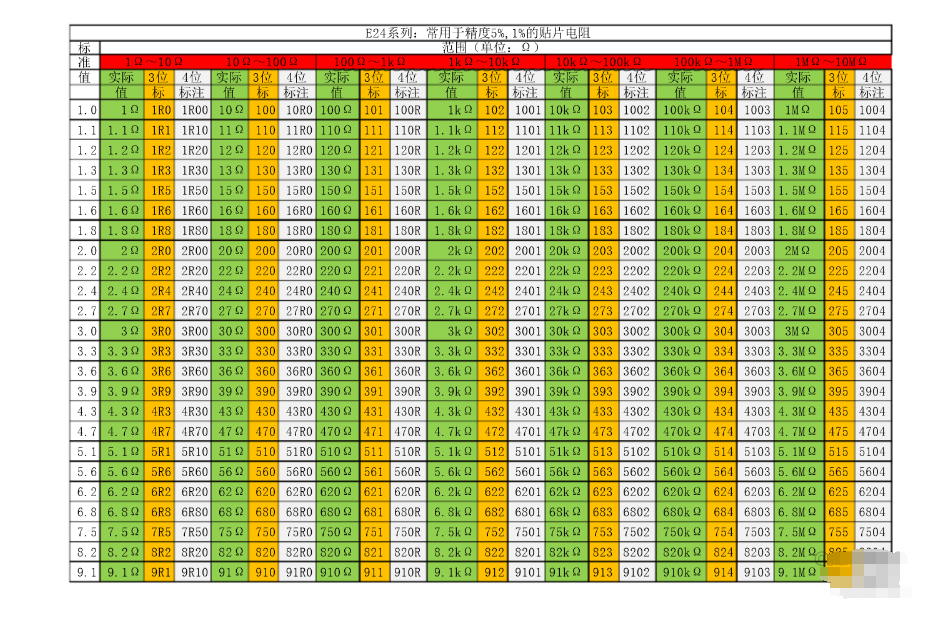

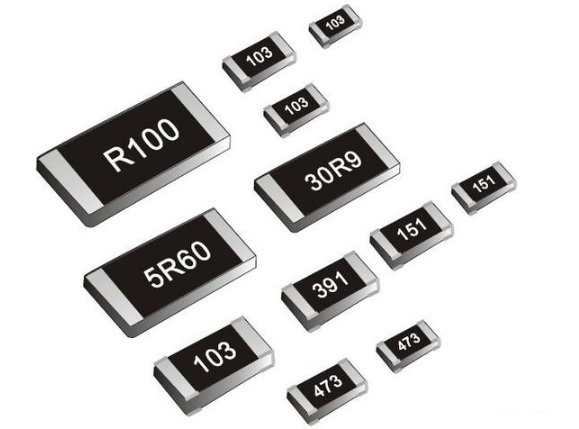

贴片电阻怎么读数?首先先了解贴片电阻阻值换算关系Ω=Ω;k= kΩ= 1,000Ω;M = MΩ= 1,000,000Ω;其次电阻阻值是指贴片电阻表面上数字代码一般标志有三位数

贴片电阻102是多少阻值

贴片电阻102是多少阻值贴片电阻阻值要怎么看-贴片电阻的阻值识别方法在电子领域很多时候都会用到贴片电阻,贴片电阻的优点非常多,比如体积小、稳定性强、装配成本不高

- 贴片电阻85c是多少阻值

85C=75kΩ。

- 如何提升环形线圈绕线电感的性能?实用技巧全解析

环形线圈绕线电感的性能优化核心要素在现代电子设备中,环形线圈绕线电感因其高效率、低电磁干扰特性而备受青睐。要充分发挥其潜力,必须从材料

空焊产生的原因及规避方法

空焊产生的原因及规避方法波峰焊空焊也被称为漏焊。电路板表面上大多数其他组件的引脚都用锡焊接,但有个别没有焊上锡。这就是线路板波峰焊空焊。波峰焊空焊的原因1.如果

- 深入理解贴片元件:如何正确区分贴片电阻与贴片二极管

贴片电阻与贴片二极管的识别与选型指南在电子工程实践中,准确识别贴片元件是确保电路稳定运行的关键。本文将从外观、参数、测试方法等多个维度

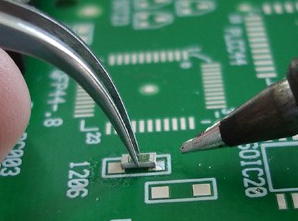

电阻焊接技巧

电阻焊接技巧1.预热。将焊机连接到电源并预热电烙铁。2.标识。电阻焊是两个平铺的接触点。贴片电阻器的尺寸非常小,其中一些只有两三根头发大,贴片电阻器已经

- 详解汽车音响电容与电阻改装:真实效果与避坑指南

汽车音响改装中的常见误区与真相随着车主对音质要求日益提高,汽车音响改装成为热门话题。其中,加装电容和调整电阻常被宣传为“提升音质”的神

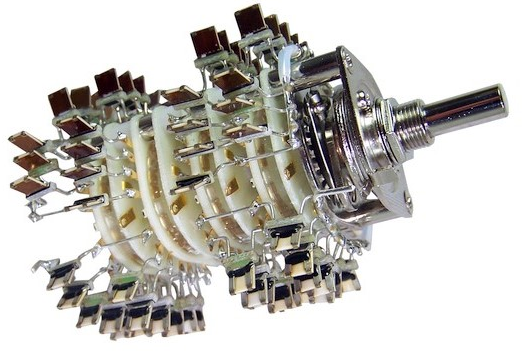

开关(步进)衰减器被动音量控制

开关(步进)衰减器被动音量控制Hi-Fi Collective 为其澳大利亚客户 Glasshouse 设计了一种具有无与伦比性能的开关衰减器无源音量控制。行业/应用领域:高端hi-fi使用的产品:Vishay箔电阻(

热敏干簧继电器的工作原理和特性

热敏干簧继电器的工作原理和特性热敏干簧继电器是一种利用热敏磁性材料检测和控制温度的新型热开关。它由热敏磁环、恒磁环、簧片管、导热安装板、塑料基板等附件

- 干电池和超级电容技术

据了解,干电池技术就是干法电极工艺技术,可以提升电池能量密度和提升电池稳定性,很明显会提升续航里程和安全性,并且可以降低成本。 再加上超