CMOS中高精度电阻的实现

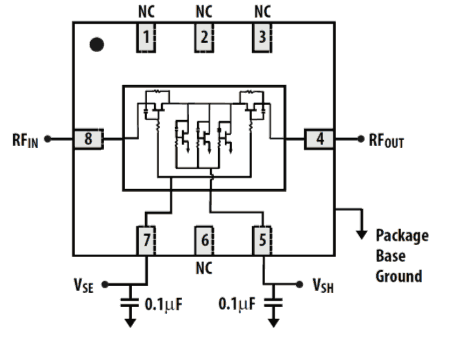

3、多参考精密电阻该电路包含一个第一电流源,其通过一个第一电流通过参考电阻器位于开或关的集成电路,以产生一个参考电压的。参考电压被施加到一个精密的高增益运算放大器的反相输入端。

第二电流源连接到第一MOS晶体管在其电阻区内工作的漏极。第二电流源也被连接到高增益运算放大器的非反相输入端。

运算放大器的输出端被电连接到第一和第二MOS晶体管的栅极。 在操作中一个精密电阻跨在第二MOS晶体管,它等于参考精密电阻位于或关闭芯片的电阻或部分可确定多个开发的。

4、互补CMOS设定偏置点获得精密电阻 甲结构具有在具有参考精密电阻(R)的(502),两个FET(520514)和滤波电容器(522),一个锁相环电路的环路滤波器(500)。电容器电压(Vbuf)被施加到两个FET的源极和R的底部充当虚拟接地。

通过滤波电容器中产生的电容器电压设定第二FET的偏置点,使得它具有集成的精密电阻器的特性。由第二FET产生的预定电压被施加到第一FET的栅极,设置第一FET的偏置点,使得它已获得相同的特性。

用于利用在一个锁相环电路的环路滤波器的建立精密的FET电阻允许在芯片上的较小的区域实现高的精度。设计结构允许实现低电容,因为电容是使用芯片上电阻的限制之一。

精度的FET电阻环路滤波器还允许用于获得电阻率和温度的更大的公差。这些大的公差,因为大的变化电阻集成电阻可以使或打破集成电路设计和温度是有益的。