如何在SPI编程期间了解时钟相位(CPHA)和时钟极性(CPOL)?

它有四根电线。在SPI通信中,总线时钟和总线相位也是两个更重要的概念。

通常,使用SPI通信时会使用默认设置,因此这两个参数很容易忽略。与您分享SPI通信,时钟极性和时钟相位的基本知识。

什么是SPI通信总线? SPI总线的英文全名是S“ Serial Periphral Interface”,其表示串行外设接口。由于通信距离较短,因此适合芯片级短距离通信。

SPI通信分为主机和从机,这是高速全双工总线通信方法。 SPI有四条线,分别是:MISO:主设备输入和从设备输出线; MISO:主设备输入和从设备输出线。

MOSI:主设备输出和从设备输入线; SCK:串行同步时钟信号线; SS:从芯片选择信号线,也以CS表示。 SPI总线的主机和从机的系统连接图如下图所示。

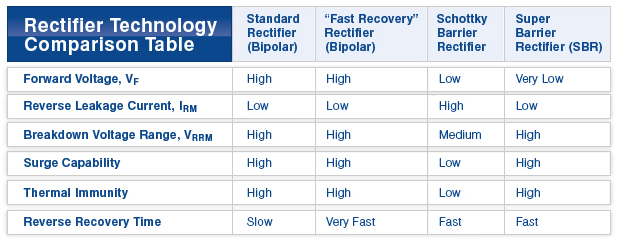

SPI总线时钟极性含义的解释SPI的时钟极性由CPOL表示。 SPI总线通信的时基参考是时钟信号线SCK。

SCK具有高电平和低电平。 SPI的时钟极性用于指示空闲时时钟信号是高电平还是低电平。

情况解释如下:当CPOL = 0时:空闲时SCK信号线为低电平;当CPOL = 0时,SCK信号线为低电平。当CPOL = 1时:空闲时SCK信号线为高;否则,SCK信号线为高。

SPI总线时钟的相位含义被解释为:时钟的相位由CPHA表示,用于决定何时在第一或第二过渡沿上对信号进行采样,以及上升沿或下降沿是由CPOL相极性表示。下面介绍两种情况。

如下所示。上图显示了CPHA = 1时的情况,即,在SCK时钟的第二个边沿对数据进行采样。

至于上升沿采样还是下降沿采样,取决于时钟极性CPOL的值。如果CPHA = 1和CPOL = 1,则在SCK时钟的第二个沿为上升沿时执行数据采样。

如果CPHA = 1且CPOL = 0,则当SCK时钟的第二个边沿为下降沿时执行数据采样。下图显示了CPHA = 0时的情况。

上图显示了CPHA = 0时的情况,也就是说,数据是在SCK时钟的第一个边沿上采样的。至于上升沿采样还是下降沿采样,取决于时钟极性CPOL的值。

如果CPHA = 0,CPOL = 1,则在SCK时钟的第一个边沿为下降沿时执行数据采样。如果CPHA = 0,CPOL = 0,则在SCK时钟的第一个边沿为上升沿时执行数据采样。

综上所述,SPI的时钟极性决定了空闲时SCK是低电平还是高电平。相位极性决定了在第一边缘或第二边缘上的数据采样。

SPI的时钟极性CPOL和相位极性CPHA是相互影响和相互决定的。以上概念可能很难理解,但是对SPI进行一次编程后,所有内容都易于理解。

-END-来源|有趣的嵌入式作者|刘小树|本文经过编译以传播相关技术,并且版权归原作者所有。 | |如果有任何侵权,请联系以将其删除| [1]国产MCU可以代替国外产品吗? MCU的未来是什么? [2] 35岁真的是程序员的障碍吗? [3]不同的编程语言有不同的能耗吗?看看这27种语言的比较! [4]为您分析超长干货:从串行端口驱动程序到Linux驱动程序模型,必定会嵌入! [5]本文绝对谈论TCP / IP!免责声明:本文内容经21ic授权后发布,版权归原作者所有。

该平台仅提供信息存储服务。本文仅代表作者的个人观点,并不代表该平台的立场。

如有任何疑问,请与我们联系,谢谢!。